# Модели в процессе проектирования сложных микроэлектронных объектов в условиях неопределенности

С. Э. Миронов<sup>1</sup>, П. М. Ширяев<sup>1</sup>, О. Ю. Кайданович<sup>2</sup>

<sup>1</sup>Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) <sup>2</sup>Карагандинский технический университет имени Абылкаса Сагинова semironovspb@yandex.ru

Аннотация. Статья посвящена рассмотрению вопросов моделирования объектов и процессов на различных этапах проектирования топологии микроэлектронных устройств. Описываются геометрические двумерные модели микроэлектронных объектов разного уровня иерархии. Рассматриваются критерии оценки моделей и способы их оптимизации.

Ключевые слова: сложные объекты микроэлектронных систем; моделирования объектов и процессов; плотноупакованное проектирование топологии интеоральных схем; размещение и трассировка; технологическая инвариантность; иерархическое сжатие топологии; согласование ячеек

# І. Введение

При изготовлении БИС используются фотошаблоны. Они строятся на основе топологических чертежей, представляющих собой геометрические двумерные модели трехмерных микроэлектронных объектов разного уровня сложности.

Основными параметрами для микроэлектронных проектов являются площадь объектов на кристалле и их время задержки. В конце прошлого века к ним добавилась технологическая инвариантность — возможность оперативной настройки проекта на требуемые проектные нормы [1]. Это позволяет накапливать топологическую проектную информацию и ускорять процесс разработки новых интегральных схем

Кроме того, сам процесс разработки технологически инвариантных описаний топологии (топологических эскизов) существенно проще, чем процесс разработки топологических чертежей. Это связано с тем, что топологический эскиз не требует детальной прорисовки, так как представляет собой абстрагированную от проектных норм модель микроэлектронного объекта.

Очевидно, что площадь на кристалле будет определяться качеством методов и средств разработки детальных топологических моделей микроэлектронных объектов — топологических чертежей. Технология их создания предполагает сборку абстрактной топологической модели и ее настройку на проектные нормы. Из ячеек в свою очередь собираются макроблоки — крупные функционально законченные фрагменты БИС.

Сборка абстрактных топологических моделей (топологических эскизов) выполняется с помощью средств размещения и трассировки [2]–[9]. Они

разделяются на графовые, комбинаторные и комбинированные. А настройка топологических эскизов на требуемые проектные нормы осуществляется с помощью средств сжатия топологии, которые также получили название средств миграции [10]—[13]. Они разделяются на графовые и сеточные.

Для иерархических микроэлектронных объектов (макроблоков БИС) организуется более сложный процесс настройки топологии на конкретные проектные нормы [14]–[16]. Во время иерархического сжатия топологии учитываются не только проектные нормы, но и габариты ячеек и координаты их выводов.

В работе рассматривается вопросы моделирования объектов и процессов на разных этапах топологического проектирования микроэлектронных объектов.

# II. МОДЕЛИ В ПРОЦЕССЕ ПРОЕКТИРОВАНИЯ СЛОЖНЫХ МИКРОЭЛЕКТРОННЫХ ОБЪЕКТОВ

Для повышения эффективности проектирования сложные системы структурируются. На разных уровнях проектирования их компоненты представляются поразному. На одних уровнях они сами выступают в качестве системы взаимодействующих компонентов. На других (более высоких) уровнях информация об их внутреннем устройстве является излишней. И тогда они представляются некий «черный ящик», взаимодействующий c внешней средой определенный интерфейс. Применительно к аппаратным решениям – через выводы.

Примечательно, что модели могут быть различными не только на разных структурно иерархических уровнях описания. На одном и том же уровне (в зависимости от решаемой на конкретном этапе задачи) объект может представляться по-разному.

В связи с этим модели можно разделять не только по структурно-иерархическому, но и функциональному признаку и по степени полноты отображения свойств объекта или процесса (позволяющей упростить решение конкретной задачи).

Микроэлектронные объекты представляют собой системы разного уровня сложности. Они состоят из внутренних компонентов (взаимодействующих, как между собой, так и с «внешней средой» объекта), границ и выводов. Можно выделить три группы объектов: транзисторы; ячейки; макроблоки.

Об особенностях их моделей речь пойдет в следующих разделах. Помимо этого, в них будут затронуты вопросы, касающиеся разработки моделей процессов генерации топологии на различных этапах ее проектирования.

### III. МОДЕЛИ ТРАНЗИСТОРОВ

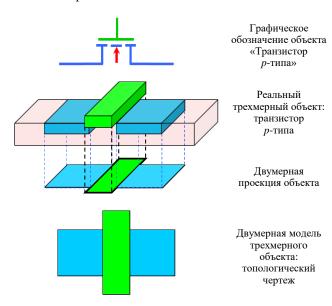

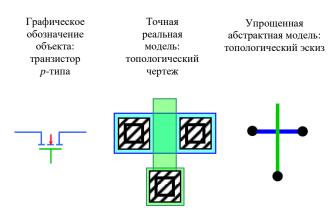

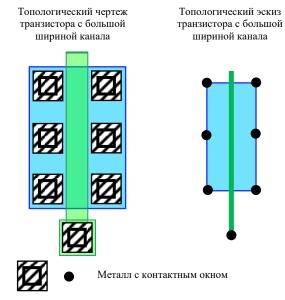

Геометрическая КМОПдвумерная модель транзистора (транзистора В технологии Комплементарный-Металл-Окисел-Полупроводник) приведена на рис. 1. Это точная геометрическая модель – топологический чертеж. В процессе проектирования используются не только реальные, но и виртуальные геометрические модели – топологические эскизы. Рис. 2 иллюстрирует связь чертежа и эскиза. Абстрактная виртуальная модель может быть и иного размера. На рис. 3 приведены топологический чертеж соответствующий топологический эскиз транзистора с большой шириной канала.

Рис. 1. Трехмерный объект «Транзистор р-типа» и его двумерная модель

Рис. 2. Двумерные модели трехмерных конструкций: «Транзистор ртипа»

Как уже было сказано, топология ячеек собирается из транзисторов методом размещения и трассировки и настраивается на требуемые проектные нормы. Подключение транзисторов друг к другу осуществляется непосредственным соединением их стоковых-истоковых областей или их соединением с помощью шин металла. Шины подключаются к

стоковым-истоковым областям и к затвору транзистора через контактные окна между ними и металлом. На рис. 3 показано, что к стокам-истокам транзистора можно подключиться в разных местах.

Рис. 3. Реальная и виртуальная двумерные модели транзистора р-типа с большой шириной канала

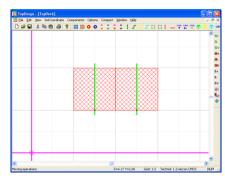

После того, как топология собрана из компонентов «транзистор» ее настраивают на заданные проектные нормы с помощью систем сжатия топологии. Алгоритмы сжатия минимизируют расстояния между частями компонентов в соответствии с технологическими требованиями предприятия—изготовителя. На рис. 4 и 5 представлены окна системы сжатия «Тор Design» [17] с топологическим эскизом и топологическим чертежом транзисторов, соединенных стоковыми-истоковыми областями.

Рис. 4. Топологический эскиз транзисторов, соединенных стоковымиистоковыми областями

Рис. 5. Топологический чертеж транзисторов, соединенных стоковыми-истоковыми областями

Из рисунка видно, что при настройке на проектные нормы системе сжатия приходится анализировать взаимное расположение перекрывающихся стоковыхистоковых областей и затворов транзисторов. Очевидно, что переход от представления топологии в виде совокупности множества транзисторов к блоку транзисторов с несколькими затворами и общей диффузионной областью стоков-истоков позволит сократить количество операций, выполняемых при сжатии топологии. Эксперименты, проведенные с использованием системы сжатия «Top Design», показали, что при таком переходе время сжатия транзисторов сокращается на 25-30 %.

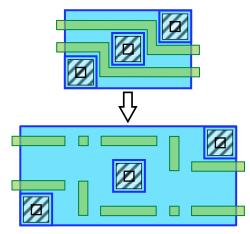

Целесообразность перехода от отдельных транзисторов к блокам транзисторов обусловлена еще одним очень важным обстоятельством. Использование блоков транзисторов с секционированием затворов [18] (рис. 6) позволяет формализовать процесс сжатия топологии ячеек с изменением формы транзисторов на виртуальной координатной сетке. Формализация [19] была осуществлена путем разработки модели процесса сжатия разработчиком-топологом, обеспечивающей как высокую плотность упаковки, так и уменьшение паразитных параметров.

Рис. 6. Блок транзисторов с секционированием затворов

Это позволяет обеспечить плотность упаковки топологии, сравнимую с плотностью упаковки ручного проектирования. Причем предложенный метод сжатия разработан для виртуальной координатной сетки, а, потому, он существенно проще методов на основе теории графов.

# IV. Модели ячеек

Ячейки является компонентами более сложного микроэлектронного объекта — макроблока БИС. Поэтому основной задачей при их проектировании является реализация процесса их согласования с соседями по габаритам и по положению выводов. Это требует реализации процессов:

- размещения и трассировки с учетом требований к размещению выводов или в стандартных ячейках, или в специализированных ячейках заказного макроблока;

- управляемого сжатия, включающего действия по мониторингу и анализу характеристик ячеек, определению требований к их габаритам и положения выводов, коррекции размеров и положения выводов.

Для решения этих задач необходима модель ячейки, описывающая лишь ее границы и выводы. В качестве примера на рис. 7 приведен топологический эскиз ячейки, а на рис. 8 текст ее спецификации – текстовой модели, описывающей ее границы и выводы (имя вывода, сторона ячейки (top, bottom, right, left), координата вывода).

Для повышения плотности упаковки в процессе согласования была [15] предложена модель ячейки, учитывающая изменения, возникающие в ее топологии в процессе согласования с соседними с ней ячейками. Это потребовало организации поэтапного итерационного процесса согласования.

Рис. 7. Пример топологического эскиза ячейки с разметкой выводов

| BRbottomlft0.00 | X_Lbtm0.50      |

|-----------------|-----------------|

| BRbottomrht0.00 | S_Ltop1.50      |

| SumBuflft1.00   | S_Lbtm1.50      |

| BRtoplft16.00   | MN_Ltop2.50     |

| SumBufrht1.00   | MN_Lbtm2.50     |

| BRtoprht16.00   | MP_Ltop7.50     |

| GND_Ltop4.50    | MP_Lbtm7.50     |

| GND_Lbtm4.50    | Y_Ltop9.50      |

| VCC_Ltop5.50    | Y_Lbtm9.50      |

| VCC_Lbtm5.50    | MP_Rtop12.50    |

| GND_Rtop15.50   | MP_Rbtm12.50    |

| GND_Rbtm15.50   | MN_Rtop17.50    |

| VCC_Rtop14.50   | MN_Rbtm17.50    |

| VCC_Rbtm14.50   | X_Rtop19.50     |

| BRleftbtm0.00   | X_Rbtm19.50     |

| BRlefttop0.00   | BRrighttop20.00 |

| X_Ltop0.50      | BRrightbtm20.00 |

Рис. 8. Пример спецификации — текстовой модели, описывающей границы и выводы ячейки

Для уменьшения времени выполнения согласования в [16] предложена технология поэтапного управляемого сжатия. Она привела к созданию модели процесса сжатия ячеек по частям. Она обеспечивает высокую плотность упаковки и малое время согласования ячеек, благодаря исключению из процесса согласования, повторяющихся процедур сжатия частей ячеек.

#### V. Модели макроблоков

Для разработки сложных иерархических объектов нужны их структурно-топологические модели, позволяющие анализировать взаимное расположение их ячеек. Это необходимо для выполнения процесса согласования соседних ячеек и для сборки точной геометрической модели макроблока — топологического чертежа.

Такая модель для регулярных матричных устройств может быть текстовой, а для нерегулярных устройств должна быть графической. В качестве примера на рис. 9 приведена структурно-топологическая модель матричного делителя.

| В  | LC  | BASC | ••• | BASC | RTC2 |

|----|-----|------|-----|------|------|

| В  | LC  | BASC |     | BASC | RTC1 |

|    |     |      |     |      |      |

| B  | LC  | BASC |     | BASC | RTC1 |

| В  | LC  | BASC |     | BASC | RBC1 |

|    |     |      |     |      |      |

|    | LC  | BASC |     | BASC | RBC1 |

| ВВ | BLC | BC   |     | BC   | RBC2 |

Рис. 9. Структурно-топологическая модель матричного делителя

Ниже приведена текстовая иерархическая структурно-топологическая модель макроблока делителя Divider.

SH2 g: B B1, 1; LC LC1, 1; BASC BASC1, 2; RTC2 RTC2, 1; SH1 g: B B2, 1; LC LC2, 1; BASC BASC2, 2; RTC1 RTC1, 1; SL1 g: B B3, 1; LC LC3, 1; BASC BASC3, 2; RBC1 RBC1, 1; SL2 g: BB BB, 1; BLC BLC, 1; BC BC, 2; RBC2 RBC2, 1; Divider v: SH2, 1; SH1, 4; SL1, 4; SL2, 1;

Модель структурирована. Она состоит из описания 4 типов горизонтальных (в описании символ «д» после имени) модулей – строк SH2, SH1, SL1, SL2. Они собираются в вертикальную конструкцию Divider (в описании символ «v» после имени). В описании строк приводится два имени ячейки: первое – имя абстрактной виртуальной модели (топологического эскиза), второе имя реальной модели (топологического чертежа). Это связано с тем, что в процессе настройки на проектные нормы происходит согласование ячеек по габаритам и положению выводов. При этом взаимное влияние ячеек друг на друга может привести к возникновению нескольких вариантов модификаций топологии одного и того же структурного компонента макроблока (ячейки). Число после имени реальной модели ячейки или строки – это коэффициент матрицирования объекта по оси абсцисс или ординат (число последовательно расположенных обеспечивающий структурную строк), параметризацию проекта (по разрядности данных).

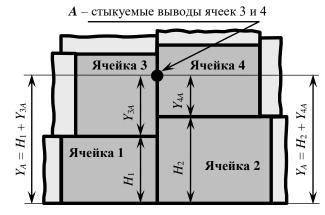

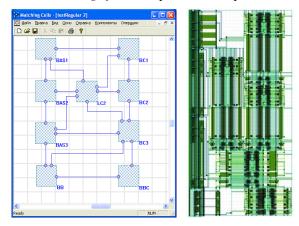

Рассмотренная модель представления сложных микроэлектронных проектов была распространена и на нерегулярные иерархические макроблоки [20]. Рис. 10 иллюстрирует расчет координат выводов ячеек в таких объектах. В рамках этой модели определение положения границ и координат выводов ячеек осуществляется с учетом суммарных размеров ранее обработанных компонентов макроблока. Использование этой модели позволило создать систему «Matching of Cells» [20] технологически иерархического инвариантного проектирования топологии макроблоков. Одним из ее структурно-топологический компонентов является редактор, позволяющий создавать модели не только регулярных, И нерегулярных иерархических макроблоков.

Рис. 10. Расчет координат выводов ячеек при их согласовании на основе структурной иерархической модели сложного нергулярного микроэлектронного объекта

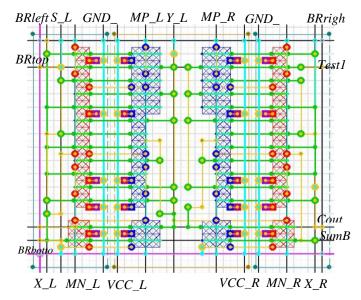

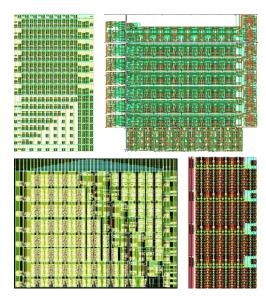

Окно редактора с примером структурной модели нерегулярного макроблока и его топология приведены на рис. 11. Примеры топологии регулярных иерархических микроэлектронных объектов, разработанных с помощью системы «Matching of Cells» приведены на рис. 12.

Рис. 11. Структурная модель нерегулярного макроблока в окне редактора системы «Matching of Cells» и полученная на ее основе топология

Рис. 12. Примеры топологии регулярных иерархических микроэлектронных объектов, разработанные с помощью системы «Matching of Cells»

#### VI. ЗАКЛЮЧЕНИЕ

Проведенный в ходе исследований анализ методов и средств проектирования сложных микроэлектронных объектов показал, что в современных условиях проекты должны разрабатываться с учетом возможно большей неопределенности. Это подразумевает комплексную параметризацию моделей объектов на [21]: структурном всех уровнях параметризации (изменение разрядности данных), топологическом (сборка топологии ячеек по выбранным схемам), схемотехническом решений), (выбор схемных электрическом (изменение ширины каналов транзисторов), технологическом (настройка проектные нормы).

Критерии эффективности методов и средств проектирования можно разделить на две группы: критерии эффективности результата проектирования и критерии эффективности процесса проектирования. Критериями эффективности результата проектирования (двумерной геометрической модели микроэлектронного объекта) являются площадь модели на кристалле и плотность ее упаковки. Они зависят от степени соответствия использованных геометрических моделей объектов и алгоритмических моделей процессов проектирования реальным объектам и процессам. К критериям эффективности процесса проектирования следует отнести простоту и удобство проектирования, и время срабатывания средств проектирования. Проведенные исследования показали, что в связи с этим на разных этапах объект может представляться разными Такая функциональная «мультимодельность» объектов позволяет обеспечивать более высокие характеристики, как результата, так и процесса проектирования. А приближение процесса генерации топологии к режиму «online» позволит путем оперативной перестройки проекта получать точные оценки геометрических характеристик макрообъектов и модифицировать оперативно макроблоки планировании и сборке топологии БИС.

#### Список литературы

- Sherwani Naveed A. Algorithms for VLSI physical design automation

print. Boston etc.: Kluwer Academic Publishers, 2002. 488 p., ISBN 0-7923-9294-9

- [2] Jo K., Kim T. Optimal Transistor Placement Combined with Global In-cell Routing in Standard Cell Layout Synthesis, 2021 IEEE 39th International Conference on Computer Design (ICCD), Storrs, CT, USA, 2021, pp. 517-524, doi: 10.1109/ICCD53106.2021.00085.

- [3] J. Chen, Z. Zhu, L. Guo, Y. -W. Tseng and Y. -W. Chang, "Mixed-Cell-Height Placement With Drain-to-Drain Abutment and Region Constraints," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 41, no. 4, pp. 1103-1115, April 2022, doi: 10.1109/TCAD.2021.3077586.

- [4] C. Duran and E. Roa, "Routing-Aware Standard Cell Placement Algorithm Applying Boolean Satisfiability," 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Korea, 2021, pp. 1-5, doi: 10.1109/ISCAS51556.2021.9401098.

- [5] Y. -L. Li, S. -T. Lin, S. Nishizawa and H. Onodera, "MCell: Multi-Row Cell Layout Synthesis with Resource Constrained MAX-SAT Based Detailed Routing," 2020 IEEE/ACM International Conference On Computer Aided Design (ICCAD), San Diego, CA, USA, 2020, pp. 1-8.

- [6] M. Cardoso, A. Bubolz, J. Cortadella, L. Rosa and F. Marques, "Transistor Placement for Automatic Cell Synthesis through Boolean Satisfiability," 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 2020, pp. 1-5, doi: 10.1109/ISCAS45731.2020.9181137.

- [7] Lu A. Simultaneous transistor pairing and placement for CMOS standard cells, 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2015, pp. 1647-1652.

- [8] N. Ryzhenko and S. Burns, "Standard cell routing via Boolean satisfiability," DAC Design Automation Conference 2012, San Francisco, CA, USA, 2012, pp. 603-612, doi: 10.1145/2228360.2228470.

- [9] Ziesemer A., Lazzar C. Transistor level automatic layout generator for non-complementary CMOS cells, 2007 IFIP International Conference on Very Large Scale Integration, Atlanta, GA, USA, 2007, pp. 116-121, doi: 10.1109/VLSISOC.2007.4402483.

- [10] Zhu J., F. Fang, Q. Tang. "Calligrapher: a new layout-migration engine for hard intellectual property libraries," IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol. 24(9), pp. 1347-1361, Sept. 2005.

- [11] De-Shiun Fu, Ying-Zhih Chaung, Yen-Hung Lin, Yih-Lang Li, "Topology-Driven Cell Layout Migration with Collinear Constraints," in International Conference on Computer Design (ICCD 2009), Squaw Creek, Lake Tahoe, California, pp. 439-444, 2009.

- [12] Shaphir E., Pinter R. Y., Wimer S., "Efficient cell-based migration of VLSI layout," 223 p. Springer Science+Business Media, New York, 2014.

- [13] Xiaoping Tang, Xin Yuan, "Technology Migration Techniques for Simplified Layouts with Restrictive Design Rules," 2006 International Conference on Computer-Aided Design (ICCAD'06), November 5-9, 2006, San Jose, CA, USA pp. 655-660

- [14] Bamji C., Varadarajan R. Leaf Cell and Hierarchical Compaction Techniques, New York – Springer Science & Business Media, LLC, Dec 6, 2012 - Technology & Engineering – 161 p., DOI 10.1007/978-1-4615-6139-2

- [15] Mironov S.E., Vasiliyev A.Yu., Safyannikov N.M. Means Of Automating The Hierarchical Design Of Complex Microelectronic Circuits With Uncertainty Of Design Rules // Problems of advanced micro- and nanoelectronic systems development (MES). SELECTED ARTICLES of the VIII All-Russia Science&Technology Conference MES-2018. Moscow. – FSFIS Institute for Design Problems in Microelectronics RAS. 2019. Pages 7-13. DOI: 10.31114/2078-7707-2019-1-7-13

- [16] Mironov S.E., Zibarev K.M. Management of Layout Matching of Objects of Complex Microelectronic Systems with Uncertainty of Design Rules // Proceedings of 2019 III International Conference on Control in Technical Systems (CTS), CTS-2019 September 2019. Pp. 69-73, DOI: 10.1109/CTS48763.2019.8973275.

- [17] Zuev I.S., Maximov A. High-Density Layout Designing of CMOS VLSI Parameterized Fragments / I.S. Zuev, A. Maximov // Proceedings of IEEE East-West Design & Test Symposium (EWDTS'10). St.Petersburg, 2010. Pp. 131–134.

- [18] Mironov S.E., Monko A.O. Geometric models of complex layout objects of microelectronic systems in advanced information technologies // Proceedings of 2017 20th IEEE International Conference on Soft Computing and Measurements, SCM 2017 July 2017. Pp. 135–138. DOI: 10.1109/SCM.2017.7970518.

- [19] Mironov S.E., Zibarev K.M. Modeling the Optimization Process of 2-Dimensional Models of 3-Dimensional Microelectronic Objects // Proceedings of 2021 IV International Conference on Control in Technical Systems (CTS), CTS-2021 September 2021. Pp. 105–108. DOI: 10.1109/CTS53513.2021.9562944.

- [20] Mironov S.E., Vasiliyev A.Yu., Safyannikov N.M. Means Of Automating The Hierarchical Design Of Complex Microelectronic Circuits With Uncertainty Of Design Rules // Problems of advanced micro- and nanoelectronic systems development (MES). SELECTED

- ARTICLES of the VIII All-Russia Science&Technology Conference MES-2018. Moscow: FSFIS Institute for Design Problems in Microelectronics RAS. 2019. Pages 7-13. DOI: 10.31114/2078-7707-2019-1-7-13

- [21] Миронов С.Э., Андреев Л.Е., Зибарев К.М. Технология комплексной параметризации топологических проектов регулярных макроблоков СБИС // ІХ Всероссийская научнотехническая конференция «Проблемы разработки перспективных микро- и наноэлектронных систем»: Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. Зеленоград, 05–08 октября 2020 г. М.: ИППМ РАН, 2020. Выпуск III. С. 35-40. DOI: 10.31114/2078-7707-2020-3-35-40